In an earlier post (# 9 ) Wptski posted a waveform that he recorded while using his ideal AFCI tester. The waveform has a peak of about 102Amps. A pulse duration of about 1 msec, and a repetition rate of 60hz.

From that post you can see that it requires at least a 75 amp level at 60hz to trip the AFCI (parallel arc). It is difficult to see the other components required in order to trip an AFCI from this diagram since they are ?hidden? in the very peak portions of the waveform. Notice how you can observe some small oscillations there?

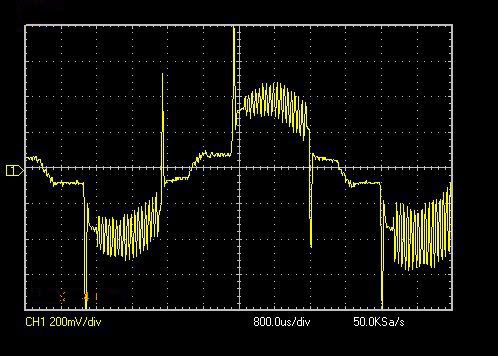

Here is a picture of the waveform I simulated in order to trip this breaker.

This is a simulated arc signature as seen by the AFCI sensing coil. You are looking at a low voltage representation of the current in the line.

The purpose of this diagram is to highlight the individual components required in the signature to trip the breaker.

What I am presenting is a combination of what I have been able to derive from reading articles on the subject along with experimentation. I have no first hand knowledge of the firmware used in these devices.

This device contains four op-amp filter circuits that need to be satisfied for the parallel arc to be recognized as follows:

1) A minimum of 75 amps present in the 60 hz portion of the waveform.

2) You can see that the 60hz component of the current is ?chopped? near zero cross. This simulates the arc extinguishing and then re-establishing itself about zero cross. This satisfies the rapid di/dt requirement.

3 & 4 ) In the peaks you can see high frequency oscillations. These are a combination of ~35Khz and ~55Kz frequencies.

A further requirement that provides for enhanced immunity to false trips is that the high frequency content -must only appear- during the peaks and not during the zero cross.

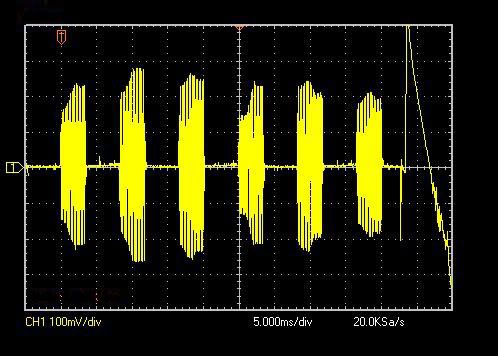

Below is a trace of one of the high frequency detection op-amp circuits outputs during an arc event. From this you can see that 6 half cycles was all that was required when presented with this simulated arc for the device to trip.

NOTE: I did not measure the time it takes for the trip solenoid to activate so it is possible that the 6th half ?cycle was not required to in order to recognize the arc.