mike_kilroy

Senior Member

- Location

- United States

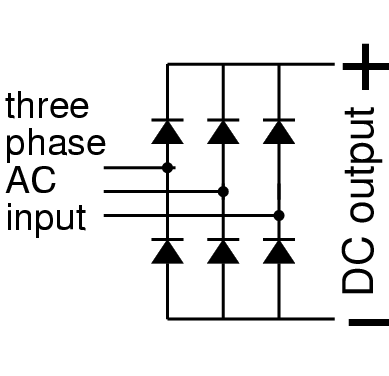

No, you are not misunderstanding. And you bring up a valid point.

1) A power factor being exhibited on the motor conductors is imminent.

2) Recommended-for-VFD motors have improved power factor characteristics,

3) but not so much that we can totally disregard it. :happyno:

Anyway, that's why I preferred to state the relationship as Pi>Po... as it takes power factor out of the equation.

4) Ii1Ø/Io3Ø > 1.732 is simply a generalization with power factor correction built in.

5) We've already heard that conversion losses raise the 1.732 factor.

6) Well, motor power factor lowers the elusive factor.

Not sure why you wrote anything in this post.

1) Please explain what is "about to happen?"

2) Nonsense!

3) Who has ever considered PF when applying a VFD?

4) Nonsense again! 1.732 has never had a thing in common with PF and never will.

5) Some folks suggested that; it has not been proven as fact.

6) What is "an elusive factor?" II call BS on this too.